## INTEGRATED CIRCUITS

Product specification Supersedes data of 1997 Oct 27 File under Integrated Circuits, IC17 1998 Jun 17

PCD5008

## **FLEX™** Pager Decoder

# CONTENTS

| CONTENT | 5                                              |

|---------|------------------------------------------------|

| 1       | FEATURES                                       |

| 2       | APPLICATIONS                                   |

| 3       | GENERAL DESCRIPTION                            |

| 4       | QUICK REFERENCE DATA                           |

| 5       | ORDERING INFORMATION                           |

| -       |                                                |

| 6       | BLOCK DIAGRAM                                  |

| 7       | PINNING                                        |

| 8       | FUNCTIONAL DESCRIPTION                         |

| 8.1     | General                                        |

| 8.2     | Clocking, reset and start-up                   |

| 8.2.1   | Oscillator                                     |

| 8.2.2   | Reset and start-up conditions                  |

| 8.3     | Serial peripheral interface (SPI)              |

| 8.3.1   | General                                        |

| 8.3.2   | SPI interconnect                               |

| 8.3.3   | SPI transfer initiated by the host             |

| 8.3.4   | SPI transfer initiated by the decoder          |

| 8.3.5   | SPI packet format                              |

| 8.3.6   | SPI timing                                     |

| 8.3.7   | Host-to-decoder packets overview               |

| 8.3.8   | Decoder-to-host packets overview               |

| 8.4     | Configuration and synchronisation              |

| 8.4.1   | General                                        |

| 8.4.2   | SPI security algorithm                         |

| 8.4.3   | Configuration sequence                         |

| 8.4.4   | Configuration packet (ID = 01H)                |

| 8.4.5   | Part ID packet (ID = FFH)                      |

| 8.4.6   | Checksum packet (ID = 00H)                     |

| 8.4.7   | Control packet (ID = 02H)                      |

| 8.4.8   | Operating the 1-minute timer                   |

| 8.4.9   | Status packet (ID = 7FH)                       |

| 8.5     | Receiver control interface                     |

| 8.5.1   | General                                        |

| 8.5.2   | Low battery detection                          |

| 8.5.3   | Receiver settings at reset                     |

| 8.5.4   | Receiver off state (ID = 10H)                  |

| 8.5.5   | Receiver warm-up sequences                     |

| 8.5.6   | Active receiver states                         |

| 8.5.7   | Forcing receiver lines (ID = 0FH)              |

| 8.5.8   | Receiver shut-down sequence                    |

| 8.6     | Configuration of the FLEX <sup>™</sup> CAPCODE |

| 8.6.1   | General                                        |

| 8.6.2   | CAPCODE format                                 |

| 8.6.3   | CAPCODE ranges                                 |

| 8.6.4   | Address calculation                            |

| 8.6.5   | Phase and frame calculation                    |

| 8.6.6   | Configuration of user addresses                |

|         | (ID = 78H, 80H to 8FH)                         |

|         |                                                |

| 8.6.7        | Configuration of assigned frames and pager                             |

|--------------|------------------------------------------------------------------------|

| 0.0.0        | collapse (ID = $20H$ to $27H$ )                                        |

| 8.6.8        | Configuration of assigned phase                                        |

| 8.7<br>8.7.1 | Call data packets<br>General                                           |

| 8.7.2        | Address packet (ID = 01H)                                              |

| 8.7.3        | Vector packets (ID = $011$ )<br>Vector packets (ID = $02$ H to $57$ H) |

| 8.7.4        | Numeric vector packet                                                  |

| 8.7.5        | Short message/tone-only vector packet                                  |

| 8.7.6        | Hex/binary, alphanumeric, secure message vectors                       |

| 8.7.7        | Short instruction vector                                               |

| 8.7.8        | Message packets (ID = 03H to 57H)                                      |

| 8.7.9        | Block Information Word (BIW) packet<br>(ID = 00H)                      |

| 8.8          | Message reception                                                      |

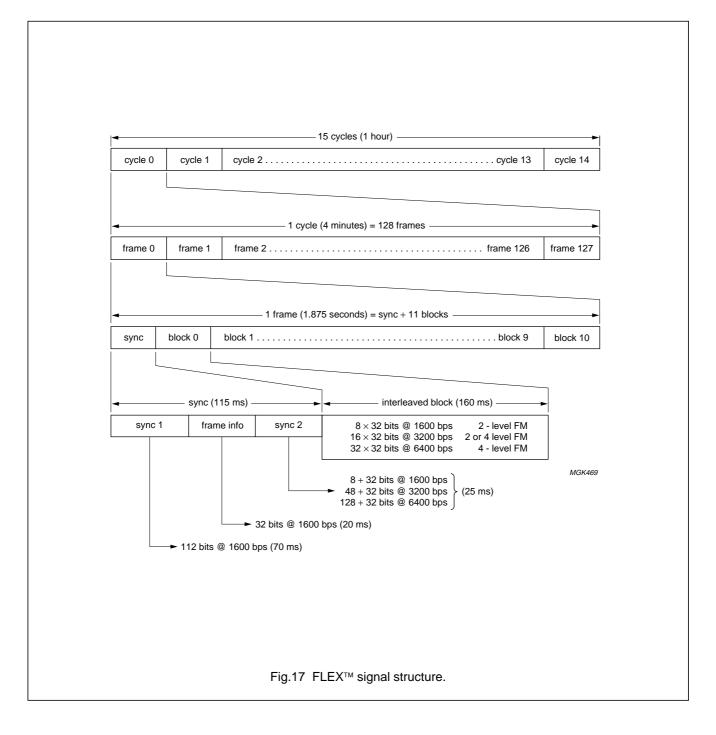

| 8.8.1        | FLEX™ signal structure                                                 |

| 8.8.2        | Message building                                                       |

| 8.8.3        | All frame mode (ID = 03H)                                              |

| 8.8.4        | Temporary addresses                                                    |

| 8.8.5        | Message fragmentation                                                  |

| 8.8.6        | Message checksums                                                      |

| 8.8.7        | Message numbering                                                      |

| 9            | LIMITING VALUES                                                        |

| 10           | DC CHARACTERISTICS                                                     |

| 11           | AC CHARACTERISTICS                                                     |

| 12           | OSCILLATOR CHARACTERISTICS                                             |

| 13           | THERMAL CHARACTERISTICS                                                |

| 14           | HANDLING                                                               |

| 15           | TEST AND APPLICATION INFORMATION                                       |

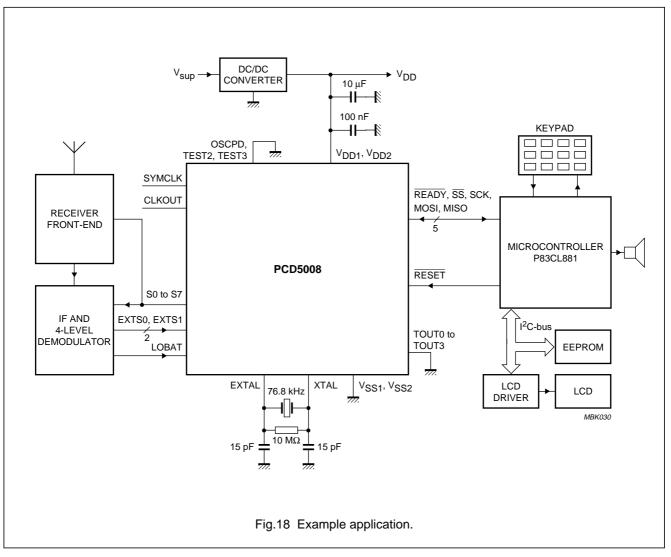

| 15.1         | Example application                                                    |

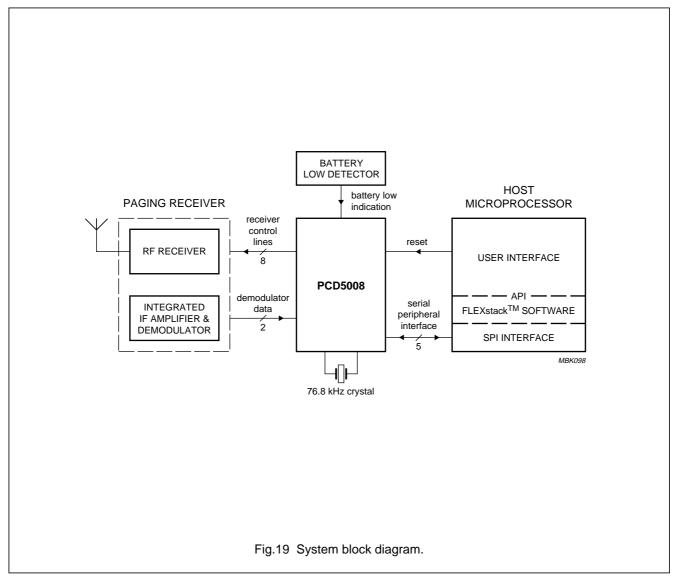

| 15.2         | System block diagram                                                   |

| 15.3         | FLEX™ encoding and decoding rules                                      |

| 15.3.1       | FLEX <sup>™</sup> encoding rules                                       |

| 15.3.2       | FLEX <sup>™</sup> decoding rules                                       |

| 16           | PACKAGE OUTLINE                                                        |

| 17           | SOLDERING                                                              |

| 17.1         | Introduction                                                           |

| 17.2         | Reflow soldering                                                       |

| 17.3         | Wave soldering                                                         |

| 17.4         | Repairing soldered joints                                              |

| 18           | DEFINITIONS                                                            |

| 19           | LIFE SUPPORT APPLICATIONS                                              |

|              |                                                                        |

### PCD5008

**GENERAL DESCRIPTION**

Motorola FLEXchip<sup>™</sup> IC.

information to the host.

This data sheet describes the operation of the PCD5008 integrated paging decoder. It is fully compatible with the

The PCD5008, also referred to as the decoder, simplifies

implementation of a FLEX™ paging device, by being able

to interface with several off-the-shelf paging receivers and

host microcontrollers/processors. Its primary function is to process information received and demodulated from a

FLEX™ radio paging channel, select messages addressed

Motorola FLEXstack™ software, installed on the product

The PCD5008 operates the paging receiver in an efficient

power consumption mode and enables the host to operate in a low-power mode when no message is being received.

host processor, communicates with the PCD5008 and

interprets the codewords that are passed to the host.

to the paging device and communicate the message

3

### 1 FEATURES

- FLEX<sup>™</sup> paging protocol signal processor

- 16 programmable user address words

- 16 fixed temporary addresses

- 1600, 3200 and 6400 bits/s decoding

- Any-phase or single-phase decoding

- Uses standard serial peripheral interface (SPI) in slave mode

- Allows low current power-down mode operation of host processor

- Highly programmable receiver control

- Real-time clock time base

- FLEX™ fragmentation and group messaging support

- Real-time clock over-the-air update support

- Compatible with synthesized receivers

- Low battery indication (external detector)

- Low cost LQFP32 plastic package

- Operates using a 76.8 kHz crystal

- Very low power consumption

- Operates at low supply voltage.

### 2 APPLICATIONS

- Numeric FLEX™ pagers

- Alphanumeric FLEX™ pagers

- Remote metering

- · Car security systems

- Personal digital assistants.

### 4 QUICK REFERENCE DATA

| SYMBOL             | PARAMETER                     | CONDITIONS             | MIN. | TYP. | MAX. | UNIT |

|--------------------|-------------------------------|------------------------|------|------|------|------|

| V <sub>DD</sub>    | supply voltage                |                        | 1.8  | 2.2  | 3.6  | V    |

| I <sub>DD</sub>    | supply current                | see Sections 10 and 12 | _    | 6.4  | _    | μΑ   |

| T <sub>amb</sub>   | operating ambient temperature |                        | -25  | +25  | +70  | °C   |

| f <sub>EXTAL</sub> | external clock frequency      |                        | _    | 76.8 | -    | kHz  |

### 5 ORDERING INFORMATION

| TYPE     |        | PACKAGE                                                                          |          |  |  |  |

|----------|--------|----------------------------------------------------------------------------------|----------|--|--|--|

| NUMBER   | NAME   | DESCRIPTION VERSION                                                              |          |  |  |  |

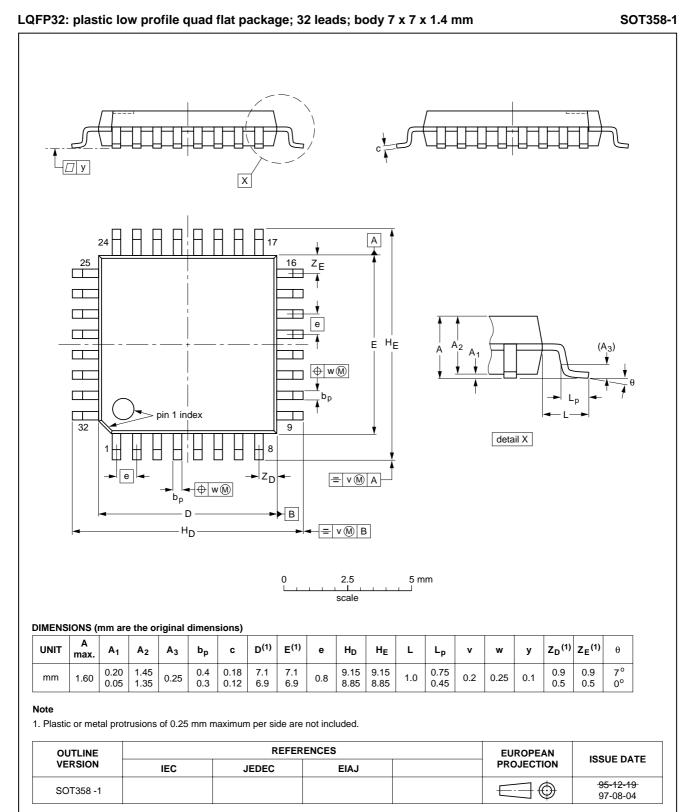

| PCD5008H | LQFP32 | plastic low profile quad flat package; 32 leads; body $7 \times 7 \times 1.4$ mm | SOT358-1 |  |  |  |

### PCD5008

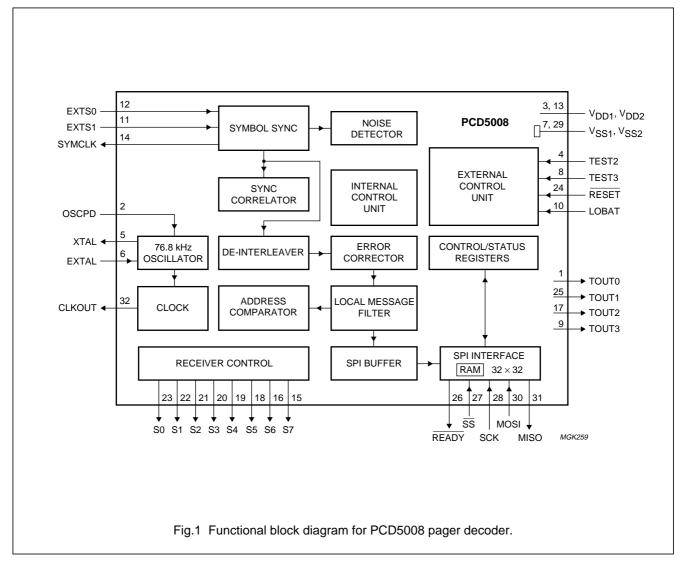

### 6 BLOCK DIAGRAM

## FLEX<sup>™</sup> Pager Decoder

### PCD5008

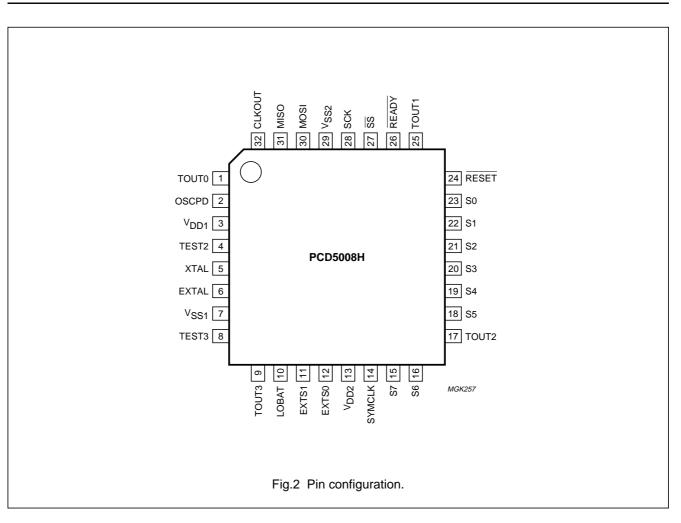

| 7 PINNING        | ì   |     |                                  |                                                                                                                                                             |

|------------------|-----|-----|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL           | PIN | I/O | PAD<br>COORDINATE<br>X/Y; note 1 | DESCRIPTION                                                                                                                                                 |

| TOUT0            | 1   | 0   | -1 405/1 088                     | 3-state test output; note 2                                                                                                                                 |

| OSCPD            | 2   | I   | -1405/816                        | internal oscillator power-down; connected to $V_{\mbox{SS}}$ when using the internal oscillator, connected to $V_{\mbox{DD}}$ when using an external source |

| V <sub>DD1</sub> | 3   | -   | -1405/563                        | supply voltage                                                                                                                                              |

| TEST2            | 4   | Ι   | -1405/306                        | manufacturing test mode input pin; has to be connected to $V_{SS}$                                                                                          |

| XTAL             | 5   | 0   | -1405/76                         | 76.8 kHz crystal oscillator output                                                                                                                          |

| EXTAL            | 6   | Ι   | -1405/-404                       | 76.8 kHz crystal oscillator input or external clock input                                                                                                   |

| V <sub>SS1</sub> | 7   | _   | -1405/-648                       | ground supply                                                                                                                                               |

| TEST3            | 8   | Ι   | -1405/-1104                      | manufacturing test mode input pin; has to be connected to $V_{SS}$                                                                                          |

| TOUT3            | 9   | 0   | -1125/-1400                      | 3-state test output; note 2                                                                                                                                 |

| LOBAT            | 10  | Ι   | -863/-1400                       | low battery voltage detect input                                                                                                                            |

| EXTS1            | 11  | Ι   | -633/-1400                       | most significant bit (MSB) of the symbol currently being decoded                                                                                            |

| EXTS0            | 12  | Ι   | -398/-1400                       | least significant bit (LSB) of the symbol currently being decoded                                                                                           |

| V <sub>DD2</sub> | 13  | _   | 134/-1400                        | supply voltage                                                                                                                                              |

| SYMCLK           | 14  | 0   | 569/-1400                        | recovered symbol clock output                                                                                                                               |

| S7               | 15  | 0   | 829/-1400                        | receiver control output port, 3-state                                                                                                                       |

| S6               | 16  | 0   | 1084/-1400                       | receiver control output port, 3-state                                                                                                                       |

| TOUT2            | 17  | 0   | 1405/-1093                       | 3-state test output; note 2                                                                                                                                 |

| S5               | 18  | 0   | 1405/-718                        | receiver control output port, 3-state                                                                                                                       |

| S4               | 19  | 0   | 1405/-398                        | receiver control output port, 3-state                                                                                                                       |

| S3               | 20  | 0   | 1 405/-93                        | receiver control output port, 3-state                                                                                                                       |

| S2               | 21  | 0   | 1 405/202                        | receiver control output port, 3-state                                                                                                                       |

| S1               | 22  | 0   | 1 405/502                        | receiver control output port, 3-state                                                                                                                       |

| S0               | 23  | 0   | 1405/812                         | receiver control output port, 3-state                                                                                                                       |

| RESET            | 24  | Ι   | 1 405/1 114                      | active LOW reset input                                                                                                                                      |

| TOUT1            | 25  | 0   | 1051/1400                        | 3-state test output; note 2                                                                                                                                 |

| READY            | 26  | 0   | 721/1400                         | output driven LOW when the PCD5008 is ready for an SPI packet                                                                                               |

| SS               | 27  | Ι   | 404/1400                         | slave select input for SPI communications                                                                                                                   |

| SCK              | 28  | I   | 149/1400                         | serial clock input for SPI communications                                                                                                                   |

| V <sub>SS2</sub> | 29  | _   | -100/1400                        | ground supply                                                                                                                                               |

| MOSI             | 30  | I   | -516/1400                        | data input for SPI communications                                                                                                                           |

| MISO             | 31  | 0   | -789/1400                        | data output for SPI communications, 3-state                                                                                                                 |

| CLKOUT           | 32  | 0   | -1084/1400                       | 38.4 kHz clock output (derived from 76.8 kHz oscillator)                                                                                                    |

### Notes

1. The pad coordinates are given in  $\mu m$  relating to the centre of the chip and are used in case of naked die delivery.

2. These test outputs may be either left unconnected or connected to  $V_{\text{SS}}$  in the application.

### 8 FUNCTIONAL DESCRIPTION

### 8.1 General

The PCD5008 simplifies implementation of a FLEX<sup>™</sup> paging device by interfacing with off-the-shelf components such as a paging receiver and a microcontroller or microprocessor (called a host). The PCD5008 is fully compatible with FLEXstack<sup>™</sup> software which provides a complete, platform independent, software driver for the PCD5008.

The PCD5008 fully supports all non-roaming aspects of the FLEX<sup>™</sup> protocol (version G1.8), and can operate in either single-phase or any-phase mode. The PCD5008 supports FLEX<sup>™</sup> dynamic grouping, allowing up to 16 temporary addresses to be enabled simultaneously. It is also capable of retrieving real time information from a FLEX<sup>™</sup> channel. The PCD5008 connects to any receiver capable of providing a 2-bit digital signal. The PCD5008 operates the paging receiver in an efficient power consumption mode. The PCD5008 has 8 receiver control lines used for warming up, operating and shutting down a receiver in stages.

The PCD5008 has the ability to detect a battery-low signal from an external detector during the receiver control sequences.

The PCD5008 carries out the following functions:

- Synchronises to a FLEX<sup>™</sup> data stream

- · Processes received, demodulated information

- Performs de-interleaving and error correction

- Selects calls addressed to the paging device using up to 16 programmable addresses

- Communicates the message information to the host.

### PCD5008

### PCD5008

The PCD5008 interfaces to a host through a serial peripheral interface (SPI). The host can then interpret the message information in an appropriate manner (numeric, alphanumeric, binary, etc.). This function is provided by the FLEXstack<sup>™</sup> software.

The PCD5008 enables the host to operate in a low power mode when no message information for the paging device is being received. It has a 38.4 kHz clock output capable of driving other devices, and has a 1-minute timer that offers low-power support for a real-time clock function on the host. The host can use receiver control lines which are not required by the receiver as expansion ports to control other peripheral devices.

### 8.2 Clocking, reset and start-up

#### 8.2.1 OSCILLATOR

The PCD5008 uses an inverting crystal oscillator. The clock signal for the internal circuitry is derived via an amplifier from the oscillator input pin EXTAL. Alternatively, an external clock signal can be fed in at input pin EXTAL. In this case the internal oscillator can be disabled by pulling the OSCPD input pin HIGH.This reduces current consumption and routes EXTAL directly to the internal clock signal. When using a crystal, an external feedback resistor and the load capacitances need to be connected to pins EXTAL and XTAL (Fig.18). See Section 12 for the recommended crystal parameters and the specification of the oscillator transconductance to guarantee correct start-up.

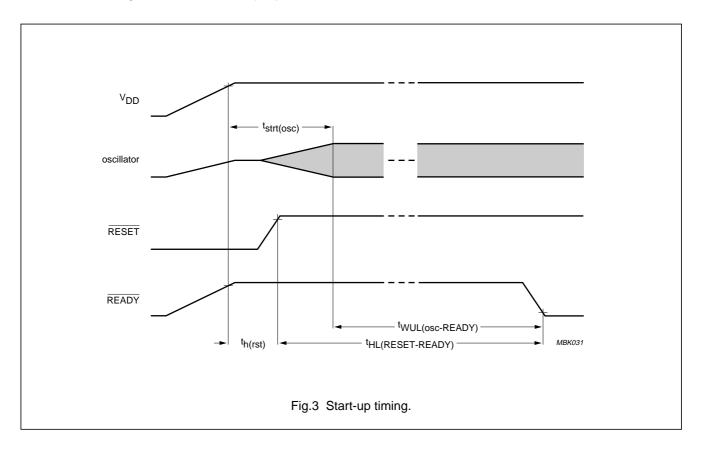

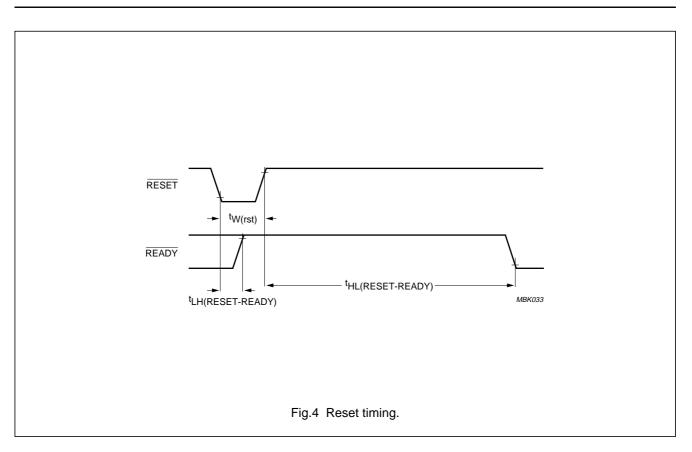

8.2.2 RESET AND START-UP CONDITIONS

The PCD5008 is reset by pulling the RESET input LOW. After releasing the RESET by pulling it HIGH, the PCD5008 counts 76800 clock cycles (typically 1 second) before pulling READY LOW to indicate that the decoder is ready for configuration via the SPI.

See Fig.3 and Section 11 for the PCD5008 timing specifications when power is applied.

See Fig.4 and Section 11 for the PCD5008 timing specifications when it is reset.

PCD5008

### FLEX<sup>™</sup> Pager Decoder

### 8.3 Serial peripheral interface (SPI)

### 8.3.1 GENERAL

All data communication between the PCD5008 and the host is done via the SPI using 32-bit data packets at data rates up to 1 Mbits/s. SPI transfers are full-duplex and can be initiated by either the host which acts as the SPI master providing the data clock for packet transfer, or the PCD5008 as an SPI slave.

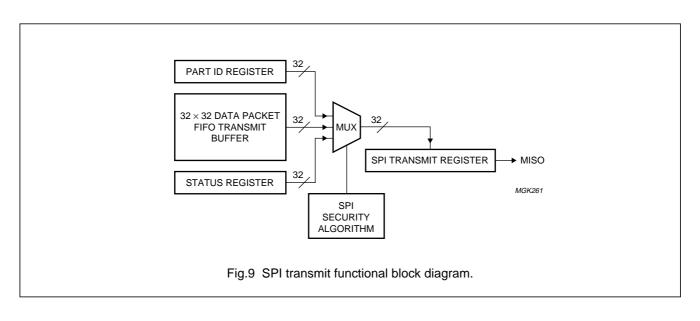

The host can send packets to configure or control the PCD5008 or a checksum packet to validate SPI communication (Section 8.4.2). The PCD5008 buffers data packets, relating to received data, into a 32 packet transmit buffer. The PCD5008 can send either a status packet, a part ID packet, or packets from the transmit buffer. In the event of a buffer overflow, the PCD5008 stops decoding and clears the transmit buffer.

### 8.3.2 SPI INTERCONNECT

Connection on the PCD5008 consists of a  $\overline{\text{READY}}$  pin and 4 SPI pins ( $\overline{\text{SS}}$ , SCK, MOSI and MISO):

READY: output signal; indicates that data is available from the PCD5008

SS: SPI select; used as PCD5008 chip select

SCK: serial clock; output from the host used for clocking data

MOSI: master output slave input; data output from the host

MISO: master input slave output; data output from the PCD5008.

### PCD5008

#### 8.3.3 SPI TRANSFER INITIATED BY THE HOST

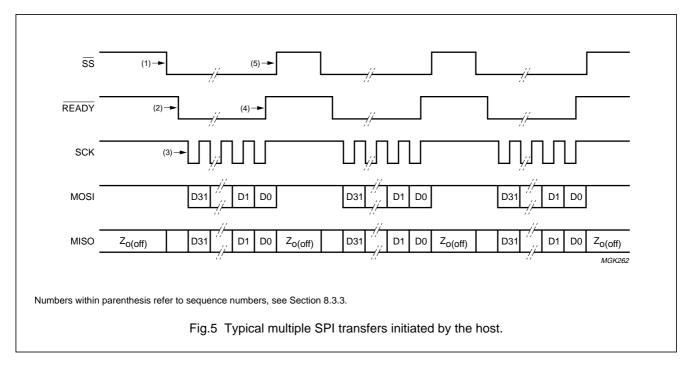

The following steps occur when the host initiates an SPI packet transfer, see Fig.5 for event timings:

- 1. The host selects the PCD5008 by driving the  $\overline{SS}$  pin LOW.

- 2. The PCD5008 indicates that it is ready to start the SPI transfer by driving the READY pin LOW.

- The host clocks each of the 32 bits of the SPI packet by pulsing SCK. Both the host and the PCD5008 sample data on the rising edge of SCK. Packets are sent MSB first.

- 4. The PCD5008 pulls the READY line HIGH, to indicate that the transfer is complete.

- 5. The host waits until the  $\overline{\text{READY}}$  line is pulled HIGH, then de-selects the PCD5008 SPI by driving the  $\overline{\text{SS}}$  pin HIGH.

- 6. The first 5 steps are repeated for each additional packet.

#### 8.3.4 SPI TRANSFER INITIATED BY THE DECODER

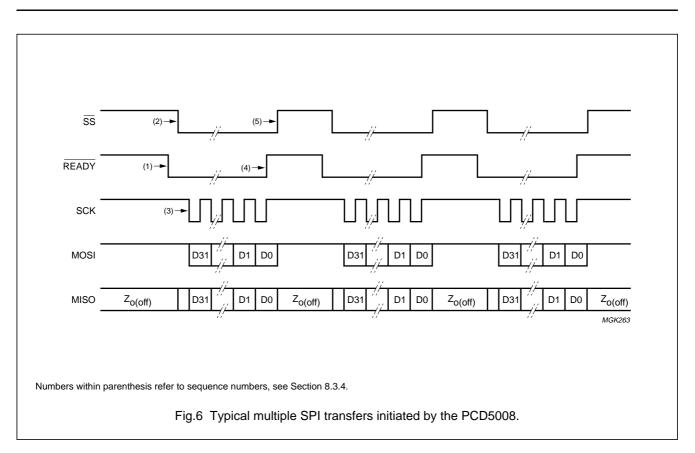

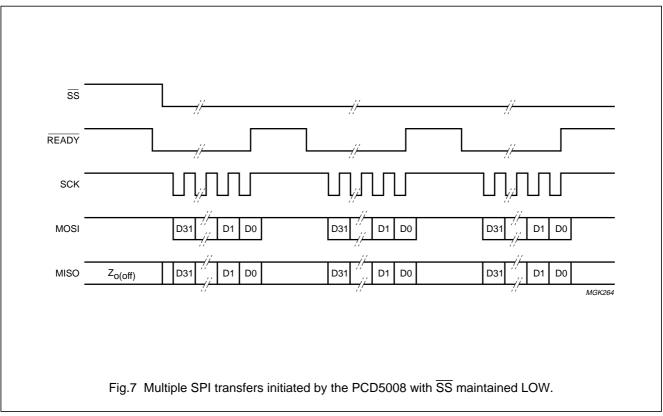

The following steps occur when the PCD5008 initiates an SPI packet transfer, see Fig.6 for event timings:

- 1. The PCD5008 initiates the SPI transfer by driving the  $$\operatorname{READY}$$  pin LOW.

- 2. If the PCD5008 is not already selected, the host selects the PCD5008 SPI by driving the  $\overline{SS}$  pin LOW.

- 3. The host clocks each of the 32 bits of the SPI packet by pulsing SCK. Both the host and the PCD5008 sample data on the rising edge of SCK. Packets are sent MSB first.

- 4. The PCD5008 pulls the READY line HIGH, to indicate that the transfer is complete.

- 5. The host may then either de-select the SPI interface of the PCD5008 (Fig.7) by driving the  $\overline{SS}$  pin HIGH or maintain  $\overline{SS}$  LOW to continue sending packets to the PCD5008.

## PCD5008

## PCD5008

### 8.3.5 SPI PACKET FORMAT

SPI data packets consist of an 8-bit ID (byte 3), followed by 24 bits of information (byte 2 to byte 0). See Table 1, note that bit 7 of byte 3 is the first bit on the bus.

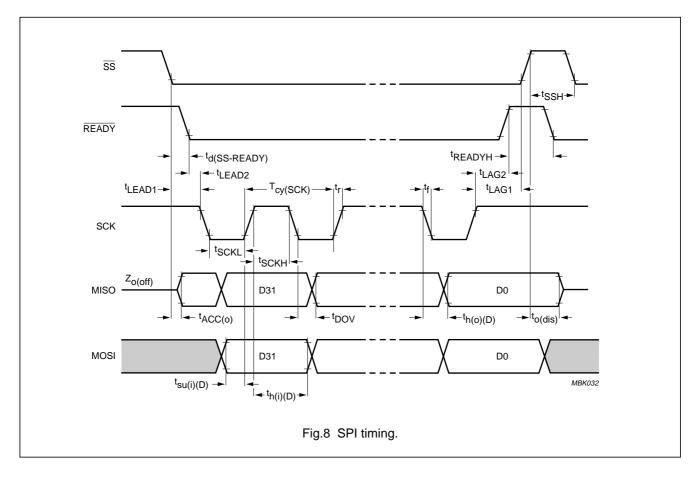

8.3.6 SPI TIMING

See Fig.8 and Chapter 11 for the timing specifications of the SPI.

| Table 1 | Packet bit assignments |

|---------|------------------------|

|---------|------------------------|

| BYTE | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| 3    | D31   | D30   | D29   | D28   | D27   | D26   | D25   | D24   |

| 2    | D23   | D22   | D21   | D20   | D19   | D18   | D17   | D16   |

| 1    | D15   | D14   | D13   | D12   | D11   | D10   | D9    | D8    |

| 0    | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

### PCD5008

#### 8.3.7 HOST-TO-DECODER PACKETS OVERVIEW

This section summarises the packets which can be sent from the host to the decoder.

| PACKET   |                                                        |         |  |

|----------|--------------------------------------------------------|---------|--|

| ID (HEX) | ТҮРЕ                                                   | SECTION |  |

| 00       | checksum                                               | 8.4.6   |  |

| 01       | configuration                                          | 8.4.4   |  |

| 02       | control                                                | 8.4.7   |  |

| 03       | all frame mode                                         | 8.8.3   |  |

| 04 to 0E | reserved (host should never send)                      | -       |  |

| 0F       | receiver line control                                  | 8.5.7   |  |

| 10       | receiver control configuration (off setting)           | 8.5.4   |  |

| 11       | receiver control configuration (warm-up 1 setting)     | 8.5.5.3 |  |

| 12       | receiver control configuration (warm-up 2 setting)     | 8.5.5.3 |  |

| 13       | receiver control configuration (warm-up 3 setting)     | 8.5.5.3 |  |

| 14       | receiver control configuration (warm-up 4 setting)     | 8.5.5.3 |  |

| 15       | receiver control configuration (warm-up 5 setting)     | 8.5.5.3 |  |

| 16       | receiver control configuration (3200 sps sync setting) | 8.5.6.2 |  |

| 17       | receiver control configuration (1600 sps sync setting) | 8.5.6.2 |  |

| 18       | receiver control configuration (3200 sps data setting) | 8.5.6.2 |  |

| 19       | receiver control configuration (1600 sps data setting) | 8.5.6.2 |  |

| 1A       | receiver control configuration (shut-down 1 setting)   | 8.5.8.1 |  |

| 1B       | receiver control configuration (shut-down 2 setting)   | 8.5.8.1 |  |

| 1C to 1F | special (ignored by decoder)                           | -       |  |

| 20       | frame assignment (frames 112 to 127)                   | 8.6.7   |  |

| 21       | frame assignment (frames 96 to 111)                    | 8.6.7   |  |

| 22       | frame assignment (frames 80 to 95)                     | 8.6.7   |  |

| 23       | frame assignment (frames 64 to 79)                     | 8.6.7   |  |

| 24       | frame assignment (frames 48 to 63)                     | 8.6.7   |  |

| 25       | frame assignment (frames 32 to 47)                     | 8.6.7   |  |

| 26       | frame assignment (frames 16 to 31)                     | 8.6.7   |  |

| 27       | frame assignment (frames 0 to 15)                      | 8.6.7   |  |

| 28 to 77 | reserved (host should never send)                      | -       |  |

| 78       | user address enable                                    | 8.6.6   |  |

| 79 to 7F | reserved (host should never send)                      | -       |  |

| 80       | user address assignment (user address 0)               | 8.6.6   |  |

| 81       | user address assignment (user address 1)               | 8.6.6   |  |

| 82       | user address assignment (user address 2)               | 8.6.6   |  |

| 83       | user address assignment (user address 3)               | 8.6.6   |  |

| 84       | user address assignment (user address 4)               | 8.6.6   |  |

| 85       | user address assignment (user address 5)               | 8.6.6   |  |

### PCD5008

| PACKET   |                                           |         |  |

|----------|-------------------------------------------|---------|--|

| ID (HEX) | ТҮРЕ                                      | SECTION |  |

| 86       | user address assignment (user address 6)  | 8.6.6   |  |

| 87       | user address assignment (user address 7)  | 8.6.6   |  |

| 88       | user address assignment (user address 8)  | 8.6.6   |  |

| 89       | user address assignment (user address 9)  | 8.6.6   |  |

| 8A       | user address assignment (user address 10) | 8.6.6   |  |

| 8B       | user address assignment (user address 11) | 8.6.6   |  |

| 8C       | user address assignment (user address 12) | 8.6.6   |  |

| 8D       | user address assignment (user address 13) | 8.6.6   |  |

| 8E       | user address assignment (user address 14) | 8.6.6   |  |

| 8F       | user address assignment (user address 15) | 8.6.6   |  |

| 90 to FF | reserved (host should never send)         | -       |  |

8.3.8 DECODER-TO-HOST PACKETS OVERVIEW

This section summarises the packets which can be sent from the PCD5008 to the host (Table 3).

### Table 3 Decoder-to-host packet ID map

| PACKET   |                                                |              |  |  |

|----------|------------------------------------------------|--------------|--|--|

| ID (HEX) | IEX) TYPE SECTION                              |              |  |  |

| 00       | block information word                         | 8.7.9        |  |  |

| 01       | address                                        | 8.7.2        |  |  |

| 02 to 57 | vector or message (ID is word number in frame) | 8.7.3, 8.7.8 |  |  |

| 58 to 7E | reserved                                       | -            |  |  |

| 7F       | status                                         | 8.4.9        |  |  |

| 80 to FE | reserved                                       | -            |  |  |

| FF       | part ID                                        | 8.4.5        |  |  |

### PCD5008

## FLEX<sup>™</sup> Pager Decoder

### 8.4 Configuration and synchronisation

#### 8.4.1 GENERAL

After a reset, all configuration data has to be (re)loaded into the PCD5008 by the host using the SPI. PCD5008 features which do not change during operation are configured using the configuration packet (Section 8.4.4), the receiver control packets (Section 8.5) and the address configuration packets (Section 8.6). PCD5008 features which can be changed during operation are configured using the control packet. The checksum packet ensures proper communication between the host and the PCD5008.

### 8.4.2 SPI SECURITY ALGORITHM

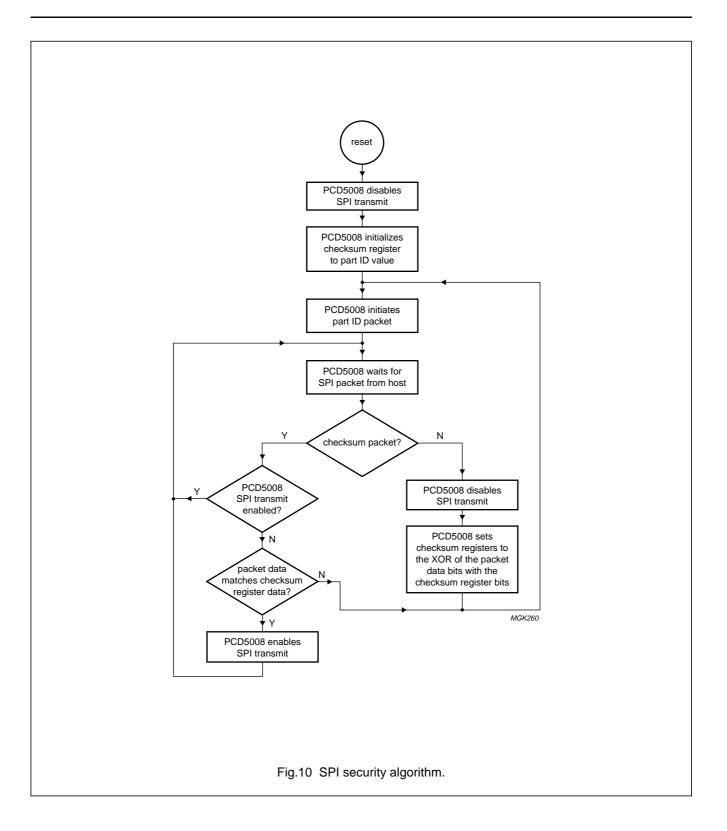

The PCD5008 provides a security algorithm to verify correct SPI operation (Figs 9 and 10). The PCD5008 maintains a checksum register equal to the result of XORing the 24 data bits of every packet it receives, except the checksum packet 00H and special packets 1CH to 1FH. When the PCD5008 is reset, the internal checksum register is initialized to the 24 bit part ID defined in the part ID packet.

Immediately following a reset and whenever the host sends a packet other than a checksum packet, the SPI output of status and data (SPI transmit) is disabled. The PCD5008 then initiates SPI transfers continuously, sending the part ID packet (Section 8.4.5). Note that when SPI transmit is disabled all decoding and timing functions are unaffected. The SPI transmit can be enabled by sending a checksum packet for which the checksum value matches the checksum register.

Any checksum packets sent when the SPI transmit is enabled, are ignored by the PCD5008 irrespective of the value of the checksum packet data bits. Thus when the PCD5008 initiates an SPI transfer and the host has no data to send, the host should send the checksum packet so as not to disable the SPI transmit. The data in the checksum packet could be a null packet (32 bit stream of all zeros).

Sending a packet other than the checksum packet when the SPI transmit is enabled causes the SPI transmit to be disabled until a checksum packet is sent with the correct value. Thus when the host re-configures the PCD5008 after a reset, the SPI transmit is disabled until the host sends a checksum packet at the end of the configuration data, with the checksum value equal to the result of XORing together the data bits of each of the configuring packets and the data bits of the part ID packet.

If the SPI transmit is enabled and there is data in the transmit buffer, the PCD5008 initiates an SPI transfer sending a packet from its transmit buffer. The PCD5008 sends the status packet (which is not buffered) when the host initiates an SPI transfer and the transmit buffer is empty.

### PCD5008

### PCD5008

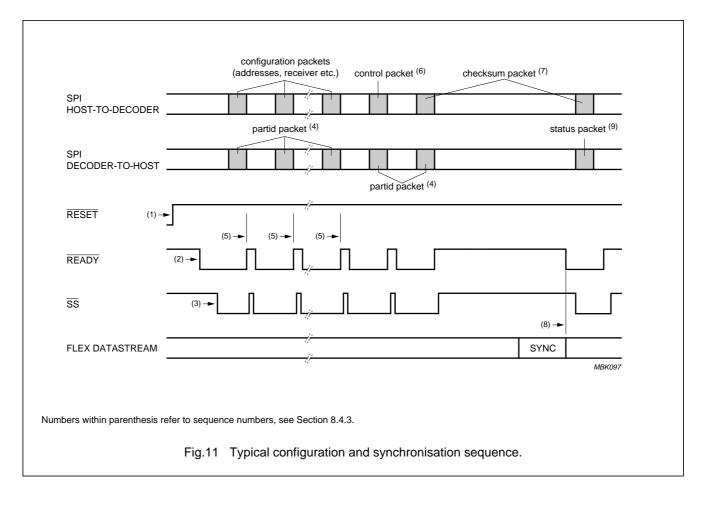

8.4.3 CONFIGURATION SEQUENCE

A typical configuration and synchronisation sequence would be as follows, see Fig.11 for event timings:

- 1. The PCD5008 is reset by the host.

- 2. After 1 second the PCD5008 interrupts the host to read the part ID by pulling the READY line LOW.

- 3. The host pulls  $\overline{SS}$  LOW at the start of each SPI transfer and clocks out the part ID data.

- 4. The host configures the following aspects of PCD5008 operation:

- a) General configuration (Section 8.4.4)

- b) Receiver operation (Section 8.5)

- c) FLEX<sup>™</sup> CAPCODE configuration (Section 8.6).

The PCD5008 writes a part ID packet in response to each incoming packet.

- 5. At the end of each packet the PCD5008 pulls the READY line HIGH, and then LOW again to indicate that packet processing is complete.

- 6. The host writes a control packet to enable FLEX<sup>™</sup> decoding in the PCD5008 (Section 8.4.7).

- 7. The host writes a checksum packet to enable SPI data output by the PCD5008 (Section 8.4.2).

- 8. On recognising a SYNC word, the PCD5008 synchronises to the channel.

- 9. The PCD5008 initiates an SPI transfer writing the status packet, indicating that it is now in synchronous mode.

### PCD5008

#### 8.4.4 CONFIGURATION PACKET (ID = 01H)

The configuration packet defines a number of different configuration options for the PCD5008. The PCD5008 ignores this packet when decoding is enabled, i.e. the ON bit in the control packet is set (Table 11).

**OFD:** oscillator frequency difference (Tables 4 and 5). These bits represent the maximum frequency difference between the 76.8 kHz oscillator (accounting for ageing, temperature variation, manufacturing tolerance etc.) and the worst case transmitter bit rate (specified in FLEX<sup>TM</sup> as  $\pm 25$  parts per million (ppm), see Section 15.3.1). For example, if the transmitter tolerance is  $\pm 25$  ppm and the 76.8 kHz oscillator tolerance is  $\pm 140$  ppm, the transmitter-oscillator frequency difference is  $\pm 165$  ppm and OFD should be cleared (300 ppm max.). Value after reset = 0. Note that configuring a smaller frequency difference in this packet results in lower power consumption due to higher receiver battery save ratios.

**SME:** synchronous mode enable (Table 5). When this bit is set, a status packet is sent automatically whenever the synchronous mode update (SMU) bit in the status packet is set. This happens whenever a change occurs in the synchronous mode (SM) status bit, which indicates that the decoder is synchronized to a FLEX<sup>TM</sup> data stream. The host can use the SM bit in the status packet as an in-range/out-of-range indication. Value after reset = 0.

**MOT:** maximum off time (Table 5). When this bit is set, the PCD5008 assumes that there can be up to 1 minute between transmitted frames on the paging system. When this bit is clear, the PCD5008 assumes that there can be up to 4 minutes between transmitted frames on the paging system. This setting is determined by the service provider. Value after reset = 0.

**COD:** clock output disable (Table 5). When this bit is clear, a 38.4 kHz signal is output on the CLKOUT pin. When this

bit is set, the CLKOUT pin is driven HIGH. Note that setting and clearing this bit can cause pulses on the CLKOUT pin that are less than one half the 38.4 kHz period. Also note that when the clock output is enabled, the CLKOUT pin always outputs the 38.4 kHz signal even when the PCD5008 is in reset. Value after reset = 0.

**MTE:** minute timer enable (Table 5). When this bit is set, a status packet is sent at one minute intervals with the minute time-out (MT) bit in the status packet set. When this bit is clear, the internal 1-minute timer stops counting. See Section 8.4.8 for details of 1-minute timer operation. Value after reset = 0.

**LBP:** low battery polarity (Table 5). This bit defines the polarity of the PCD5008's LOBAT pin: When this bit is set, a HIGH at input LOBAT represents a low battery condition. The LB bit in the status packet is initialized to the inverse (i.e. inactive) value of the LBP bit when the PCD5008 is turned on (by setting the ON bit in the control packet). When the PCD5008 is turned on, the first low battery update in the status packet is sent to the host when a low battery condition is detected on the LOBAT pin. Value after reset = 0.

**SP:** signal polarity (Tables 5, 6 and 7). These bits set the polarity of EXTS1 and EXTS0 input signals. The polarity of the EXTS1 and EXTS0 bits is determined by the receiver design. Value after reset = 0.

| OFD <sub>1</sub> | OFD <sub>0</sub> | FREQUENCY DIFFERENCE<br>(ppm) |

|------------------|------------------|-------------------------------|

| 0                | 0                | ±300                          |

| 0                | 1                | ±150                          |

| 1                | 0                | ±75                           |

| 1                | 1                | ±0                            |

| Table 4 | Maximum | oscillator | frequency | difference |

|---------|---------|------------|-----------|------------|

|---------|---------|------------|-----------|------------|

| Table 5 | Configuration packet bit assignments |

|---------|--------------------------------------|

|---------|--------------------------------------|

| BYTE | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1            | BIT 0            |

|------|-------|-------|-------|-------|-------|-------|------------------|------------------|

| 3    | 0     | 0     | 0     | 0     | 0     | 0     | 0                | 1                |

| 2    | 0     | 0     | 0     | 0     | 0     | 0     | OFD <sub>1</sub> | OFD <sub>0</sub> |

| 1    | 0     | 0     | 0     | 0     | 0     | 0     | SP1              | SP0              |

| 0    | SME   | MOT   | COD   | MTE   | LBP   | 0     | 0                | 0                |

#### Table 6Input signal polarity

| ер              | ер              | SIGNAL POLARITY |          |  |  |

|-----------------|-----------------|-----------------|----------|--|--|

| SP <sub>1</sub> | SP <sub>0</sub> | EXTS1           | EXTS0    |  |  |

| 0               | 0               | normal          | normal   |  |  |

| 0               | 1               | normal          | inverted |  |  |

| 1               | 0               | inverted        | normal   |  |  |

| 1               | 1               | inverted        | inverted |  |  |

Table 7 FLEX™ 4 level FSK modulation selection

| EXTS1 | EXTS0 | FSK MODULATION<br>AT SP = 0,0<br>(Hz) |

|-------|-------|---------------------------------------|

| 1     | 0     | +4800                                 |

| 1     | 1     | +1600                                 |

| 0     | 1     | -1600                                 |

| 0     | 0     | -4800                                 |

#### Table 8 Part ID packet bit assignments

8.4.5 PART ID PACKET (ID = FFH)

The part ID packet is output by the PCD5008 SPI whenever the SPI transmit is disabled due to the checksum feature.

MDL: model (Table 8). The PCD5008 model value is 0.

**CID:** compatibility ID (Table 8). This value describes other parts with the same model number, which are compatible with this part. The PCD5008 compatibility value is 1. Devices which implement a superset of PCD5008 functionality have MDL cleared and CID<sub>0</sub> set.

**REV:** revision (Table 8). This identifies the manufacturing version of the PCD5008. For the PCD5008 the value is 6. Compatible parts have values in the range 0 to 5.

8.4.6 CHECKSUM PACKET (ID = 00H)

See Table 9 for checksum packet bit assignment.

CV: checksum value (24 bits), see Section 8.4.2.

| BYTE | BIT 7            | BIT 6            | BIT 5             | BIT 4             | BIT 3             | BIT 2             | BIT 1            | BIT 0            |

|------|------------------|------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 3    | 1                | 1                | 1                 | 1                 | 1                 | 1                 | 1                | 1                |

| 2    | MDL <sub>1</sub> | MDL <sub>0</sub> | CID <sub>13</sub> | CID <sub>12</sub> | CID <sub>11</sub> | CID <sub>10</sub> | CID <sub>9</sub> | CID <sub>8</sub> |

| 1    | CID <sub>7</sub> | CID <sub>6</sub> | CID <sub>5</sub>  | CID <sub>4</sub>  | CID <sub>3</sub>  | CID <sub>2</sub>  | CID <sub>1</sub> | CID <sub>0</sub> |

| 0    | REV <sub>7</sub> | REV <sub>6</sub> | REV <sub>5</sub>  | REV <sub>4</sub>  | REV <sub>3</sub>  | REV <sub>2</sub>  | REV <sub>1</sub> | REV <sub>0</sub> |

Table 9

Checksum packet bit assignments

| BYTE | BIT 7            | BIT 6            | BIT 5            | BIT 4            | BIT 3            | BIT 2            | BIT 1            | BIT 0            |

|------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 3    | 0                | 0                | 0                | 0                | 0                | 0                | 0                | 0                |

| 2    | CV <sub>23</sub> | CV <sub>22</sub> | CV <sub>21</sub> | CV <sub>20</sub> | CV <sub>19</sub> | CV <sub>18</sub> | CV <sub>17</sub> | CV <sub>16</sub> |

| 1    | CV <sub>15</sub> | CV <sub>14</sub> | CV <sub>13</sub> | CV <sub>12</sub> | CV <sub>11</sub> | CV <sub>10</sub> | CV <sub>9</sub>  | CV <sub>8</sub>  |

| 0    | CV7              | CV <sub>6</sub>  | CV <sub>5</sub>  | CV <sub>4</sub>  | CV <sub>3</sub>  | CV <sub>2</sub>  | CV <sub>1</sub>  | CV <sub>0</sub>  |

### PCD5008

### PCD5008

#### 8.4.7 CONTROL PACKET (ID = 02H)

The control packet defines a number of different control bits for the PCD5008.

**FF:** force frame 0 to 7 (Table 11). When set, each of these bits forces the PCD5008 to decode one of the FLEX<sup>TM</sup> frames 0 to 7 irrespective of the system collapse value (for details of collapse values see Section 8.6.2). For example, if the system collapse causes the PCD5008 to decode frames 0, 32, 64 and 96, setting FF<sub>2</sub> causes the PCD5008 to also decode FLEX<sup>TM</sup> frame 2. This may be used to acquire transmitted time information. Value after reset = 0.

**SPM:** single phase mode (Table 11). When this bit is set, the PCD5008 decodes only one of the transmitted phases. When this bit is clear, the PCD5008 decodes all transmitted phases. This value is determined by the CAPCODE (Section 8.6). A change to this bit while the PCD5008 is on does not take effect until the next block 0 of a frame. Value after reset = 0.

**PS:** phase select (Tables 10 and 11). When the SPM bit is set, these bits define which phase the PCD5008 shall decode. This value is determined by the CAPCODE (Section 8.6). A change to these bits, while the PCD5008 is on, does not take effect until the next block 0 of a frame. Value after reset = 0.

| PS₁ | PS <sub>0</sub> | DECODED PHASE (BASED ON<br>FLEX™ DATA RATE) |             |   |  |  |

|-----|-----------------|---------------------------------------------|-------------|---|--|--|

|     |                 | 1600 bits/s                                 | 6400 bits/s |   |  |  |

| 0   | 0               | А                                           | А           | А |  |  |

| 0   | 1               | А                                           | А           | В |  |  |

| 1   | 0               | A                                           | С           | С |  |  |

| 1   | 1               | А                                           | С           | D |  |  |

Table 10 Phase selection (PS bits)

**SBI:** send block information words (BIW) 2 to 4 (Table 11). When this bit is set, BIWs with time and date information and BIWs received in error are sent to the host, (Section 8.7.9). Value after reset = 0.

**MTC:** minute timer clear (Table 11). Setting this bit causes the 1-minute timer to restart from 0 (Section 8.4.8).

**ON:** turn on decoder (Table 11). When this bit is set, the PCD5008 decodes FLEX<sup>™</sup> signals. If this bit is cleared, signal processing stops. However, to assure proper operation, the PCD5008 requires that it be set into asynchronous mode when turned off. To achieve that the following sequence must be used:

- 1. Send control packet with ON bit clear (decoder off)

- 2. Send control packet with ON bit set (decoder on)

- 3. Send control packet with ON bit clear (decoder off).

Timing between these steps is specified below and is measured from the positive edge of the last clock of one packet to the positive edge of the last clock of the next packet.

- The minimum time between steps 1 and 2 is the greater of 2 ms or the programmed shut-down time. The programmed shut-down time is the sum of all of the times programmed in the used receiver shut-down settings packets.

- There is no maximum time between steps 1 and 2

- The minimum time between steps 2 and 3 is 2 ms

- The maximum time between steps 2 and 3 is the programmed warm-up time minus 2 ms. The programmed warm-up time is the sum of all the times programmed in the used receiver warm-up settings packets.

#### 8.4.8 OPERATING THE 1-MINUTE TIMER

The PCD5008 provides a 1-minute timer which allows the host to implement a time-of-day function while maintaining low-power operation. The 1-minute timer is enabled using the MTE bit in the configuration packet (Section 8.4.4). When the 1-minute timer is enabled, a status packet is sent at 1-minute intervals with the MT bit set (Section 8.4.9). When the MTE bit is clear, the internal 1-minute timer stops counting. When the host sends a control packet with MTC bit set, the 1-minute timer restarts from 0. This allows accurate setting of a time-of-day function.

| BYTE | BIT 7           | BIT 6  | BIT 5           | BIT 4           | BIT 3           | BIT 2           | BIT 1           | BIT 0           |

|------|-----------------|--------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 3    | 0               | 0      | 0               | 0               | 0               | 0               | 1               | 0               |

| 2    | FF <sub>7</sub> | $FF_6$ | $FF_5$          | FF <sub>4</sub> | FF <sub>3</sub> | FF <sub>2</sub> | FF <sub>1</sub> | FF <sub>0</sub> |

| 1    | 0               | SPM    | PS <sub>1</sub> | PS <sub>0</sub> | 0               | 0               | 0               | 0               |

| 0    | 0               | SBI    | 0               | MTC             | 0               | 0               | 0               | ON              |

Table 11

Control packet bit assignments

## PCD5008

### 8.4.9 STATUS PACKET (ID = 7FH)

The status packet contains various types of information that the host may require and is sent to the host:

- Whenever the PCD5008 is polled and has no other data to send

- On events for which the PCD5008 is configured to send the status packet (Sections 8.4.4 and 8.4.7). In this case, the PCD5008 prompts the host to read a status packet for the following conditions:

- SMU bit in the status packet and the SME bit in the configuration packet are set

- MT bit in the status packet and the MTE bit in the configuration packet are set

- EOF bit in the status packet is set

- LBU bit in the status packet is set

- BOE bit in the status packet is set.

**FIV:** frame information valid (Table 12). This bit is set, when a valid frame information word has been received since becoming synchronous to the system and the f and c fields contain valid values. If this bit is clear, no valid frame information words have been received since the PCD5008 became synchronous to the system. This value changes from 0 to 1 at the end of block 0 (Fig.17) of the frame in which the first frame information word was properly received. It is cleared when the PCD5008 goes into asynchronous mode (see SM bit below). This bit is initialized to 0 when the PCD5008 is reset and when the PCD5008 is turned off by clearing the ON bit in the control packet.

**f:** current frame number (Table 12). This value is updated every frame regardless of whether the PCD5008 needs to decode the frame. This value changes to its proper value for a frame at the end of block 0 of the frame. The value of these bits is not guaranteed when FIV is 0.

**c:** current system cycle number (Table 12). This value is updated every frame regardless of whether the PCD5008 needs to decode the frame. This value changes to its proper value for a frame at the end of block 0 of the frame. The value of these bits is not guaranteed when FIV is 0.

**SM:** synchronous mode (Table 12). This bit is set, when the PCD5008 is synchronous to the system.

The PCD5008 sets this bit when the first synchronization words are received. It clears this bit when synchronisation to the FLEX<sup>™</sup> signal is lost. This bit is initialized to 0 when the PCD5008 is reset and when it is turned off by clearing the ON bit in the control packet.

**SMU:** synchronous mode update (Table 12). This bit is set if the SM bit has been updated in this packet. After the PCD5008 has been turned on, this bit is set when the first synchronization words are found (SM changes to 1) or when the first synchronization search period (meaning the receiver is active during this time) expires (SM stays 0), after the PCD5008 is turned on. The latter condition gives the host the option of assuming the paging device is in range when it is turned on, and displaying out-of-range only after the initial search period expires. After the initial synchronous mode update, the SMU bit is set whenever the PCD5008 switches from/to synchronous mode. The bit is cleared when read. Changes in the SM bit due to turning off the PCD5008 does not set the SMU bit. This bit is initialized to 0 when the PCD5008 is reset.

**LB:** low battery (Table 12). Set to the value last read from the LOBAT pin. The host controls when the LOBAT pin is read via the receiver control packets. This bit is initialized to 0 at reset. It is also initialized to the inverse of the LBP bit in the configuration packet, when the PCD5008 is turned on, by setting the ON bit in the control packet.

**LBU:** low battery update (Table 12). This bit is set if the value on two consecutive reads of the LOBAT pin yielded different results. The bit is cleared when read. The host controls when the LOBAT pin is read via the receiver control packets. Changes in the LB bit due to turning on the PCD5008 do not cause the LBU bit to be set. This bit is initialized to 0 when the PCD5008 is reset.

**MT:** minute time-out (Table 12). Set if one minute has elapsed. The bit is cleared when read. This bit is initialized to 0 when the PCD5008 is reset.

**EOF:** end of frame (Table 12). Set when the PCD5008 is in all frame mode (AFM) (Section 8.8.3), and the end of the frame has been reached. The PCD5008 is in the AFM if the AFM enable counter is non-zero, if any temporary address enabled (TAE) counter is non-zero (Section 8.8.3) or if the FAF bit in the AFM packet is set. The bit is cleared when read and initialized to 0 when the PCD5008 is reset.

**BOE:** buffer overflow error (Table 12). Set when information has been lost owing to slow host response time. When the PCD5008 detects that its SPI transmit buffer has overflowed, it clears the transmit buffer, turns off decoding by clearing the ON bit in the control packet, and sets this bit. The bit is cleared when read. This bit is initialized to 0 when the PCD5008 is reset.

**x:** unused bits (Table 12). The value of these bits is not guaranteed.

### PCD5008

#### 8.5 Receiver control interface

#### 8.5.1 GENERAL

The PCD5008 has 8 programmable receiver control lines, S0 to S7. The host can program via SPI packets what setting is applied to the receiver control lines, the duration of warm-up and shut-down stages and the polling of the LOBAT pin. This programmability allows the PCD5008 to interface with many off-the-shelf receiver ICs. Note that these packets are ignored when sent while decoding is enabled (ON bit is set in the control packet).

#### 8.5.2 LOW BATTERY DETECTION

The PCD5008 can be configured to poll the LOBAT pin at the end of every receiver control setting. This check can be enabled or disabled for each receiver control setting. If the poll is enabled for a setting, the pin is read just before the PCD5008 activates the next setting on the receiver control lines. The PCD5008 sends a status packet whenever the value differs from the previous time that the LOBAT pin was polled.

#### 8.5.3 RECEIVER SETTINGS AT RESET

Table 12 Status packet bit assignments

The receiver control ports are 3-state outputs which are set to high impedance when the PCD5008 is reset, until the corresponding FRS bit in the receiver line control packet is set or the PCD5008 is turned on for the first time after a reset (by setting the ON bit in the control packet). This allows the designer to force the receiver control lines to the receiver off setting with external pull-up or pull-down resistors before the host can configure these settings in the PCD5008.

#### 8.5.4 RECEIVER OFF STATE (ID = 10H)

The receiver off state is configured by the receiver off setting packet (Table 13), which defines the settings to be applied when the PCD5008 decides to switch the receiver off.

**LBC:** low battery check (Table 13). If this bit is set, the PCD5008 checks the status of the LOBAT port just before leaving the receiver off state. Value after reset = 0.

**CLS:** control line setting (Table 13). This is the value to be output on the receiver control lines for the receiver off state. Value after reset = 0.

**ST**: step time (Table 13). This sets the duration of the warm-up off time. The setting is in steps of 625  $\mu$ s. Valid values are 625  $\mu$ s (ST = 01H) to 159.375 ms (ST = FFH). Value after reset = 01H.

| BYTE | BIT 7 | BIT 6          | BIT 5          | BIT 4          | BIT 3          | BIT 2          | BIT 1          | BIT 0          |

|------|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 3    | 0     | 1              | 1              | 1              | 1              | 1              | 1              | 1              |

| 2    | FIV   | f <sub>6</sub> | f <sub>5</sub> | f <sub>4</sub> | f <sub>3</sub> | f <sub>2</sub> | f <sub>1</sub> | f <sub>0</sub> |

| 1    | SM    | LB             | х              | х              | с <sub>3</sub> | C <sub>2</sub> | С <sub>1</sub> | C <sub>0</sub> |

| 0    | SMU   | LBU            | х              | MT             | х              | EOF            | х              | BOE            |

Table 13 Receiver off setting packet bit assignments

| BYTE | BIT 7            | BIT 6            | BIT 5            | BIT 4            | BIT 3            | BIT 2            | BIT 1            | BIT 0            |

|------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 3    | 0                | 0                | 0                | 1                | 0                | 0                | 0                | 0                |

| 2    | 0                | 0                | 0                | 0                | LBC              | 0                | 0                | 0                |

| 1    | CLS <sub>7</sub> | CLS <sub>6</sub> | CLS <sub>5</sub> | CLS <sub>4</sub> | CLS <sub>3</sub> | CLS <sub>2</sub> | CLS <sub>1</sub> | CLS <sub>0</sub> |

| 0    | ST <sub>7</sub>  | ST <sub>6</sub>  | ST <sub>5</sub>  | ST <sub>4</sub>  | ST <sub>3</sub>  | ST <sub>2</sub>  | ST <sub>1</sub>  | ST <sub>0</sub>  |

## PCD5008

#### 8.5.5 RECEIVER WARM-UP SEQUENCES

#### 8.5.5.1 Normal receiver warm-up sequence

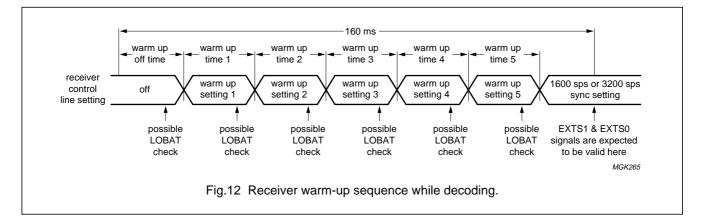

The PCD5008 allows for up to 6 steps associated with warming up the receiver. When the PCD5008 turns on the receiver while decoding, it starts the warm-up sequence 160 ms before it requires valid signals at the EXTS1 and EXTS0 input pins.

- 1. The PCD5008 leaves the receiver control lines in the off state for the programmed warm-up off time.

- The first warm-up setting, if enabled, is applied to the receiver control lines for the amount of time programmed for that setting.

- 3. Subsequent warm-up settings are applied to the receiver control lines for their corresponding time until a disabled warm-up setting is found.

- At the end of the last used warm-up setting, the 1600 symbols per second (sps) sync setting or the 3200 sps sync setting is applied to the receiver control lines depending on the PCD5008 current state.

The PCD5008 must be configured such that the sum of all of the used warm-up times and the warm-up off time does not exceed 160 ms.

If it exceeds 160 ms, the PCD5008 executes the receiver shut-down sequence 160 ms after the start of the warm-up off time. If the sum of all of the used warm-up times and the warm-up off times is less than 160 ms, the receiver remains in the 1600 sps sync setting or the 3200 sps sync setting from the end of the last used warm-up setting until valid signals are expected (160 ms after the start of the warm-up off time). Figure 12 shows the receiver warm-up sequence while decoding, when all warm-up settings are enabled.

#### 8.5.5.2 First receiver warm-up sequence

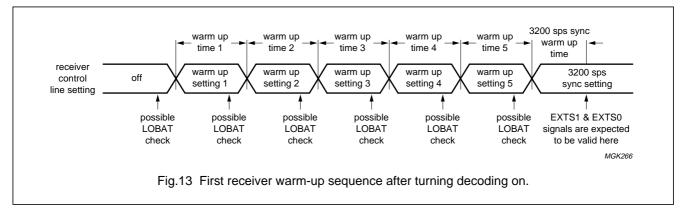

When the PCD5008 is turned on by setting the ON bit in the control packet, the receiver warm-up sequence differs from the sequence described in Section 8.5.5.1. After the ON bit is set no receiver warm-up off time is applied, instead the PCD5008 immediately begins to apply the receiver warm-up settings. When a disabled warm-up setting is found, the decoder applies 3200 sps sync setting to the receiver control lines. The decoder then expects valid signals after the 3200 sps sync warm-up time. Figure 13 shows the receiver warm-up sequence when the PCD5008 is first turned on and when all warm-up settings are enabled.

### PCD5008

#### 8.5.5.3 Receiver warm-up setting packets (ID = 11H to 15H)

**CLS:** control line setting (Table 15). This is the value to be output on the receiver control lines (S0 to S7) for this receiver warm-up state. Value after reset = 0.

**SE:** step enable (Table 15). The receiver setting is enabled when the bit is set. If the bit is cleared then that step in the receiver warm-up sequence is disabled and all following steps are ignored. Value after reset = 0.

**LBC:** low battery check (Table 15). If this bit is set, the PCD5008 checks the status of the LOBAT port just before leaving this receiver warm-up state. Value after reset = 0.

**ST:** step time (Table 15). This sets the duration time for receiver warm-up until the next receiver state. The setting is in 625  $\mu$ s steps and valid values are:

625  $\mu$ s (ST = 01H) to 79.375 ms (ST = 7FH).

Value after reset = 01H.

**s:** setting number, see Tables 14 and 15 for the s names and values and location in the receiver warm-up packet.

| Table 14 | Receiver | warm-up | setting | numbers |

|----------|----------|---------|---------|---------|

|----------|----------|---------|---------|---------|

| S <sub>3</sub> | S <sub>2</sub> | s <sub>1</sub> | S <sub>0</sub> | SETTING NAME |

|----------------|----------------|----------------|----------------|--------------|

| 0              | 0              | 0              | 1              | warm-up 1    |

| 0              | 0              | 1              | 0              | warm-up 2    |

| 0              | 0              | 1              | 1              | warm-up 3    |

| 0              | 1              | 0              | 0              | warm-up 4    |

| 0              | 1              | 0              | 1              | warm-up 5    |

| BYTE | BIT 7            | BIT 6            | BIT 5            | BIT 4            | BIT 3            | BIT 2            | BIT 1            | BIT 0            |

|------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 3    | 0                | 0                | 0                | 1                | s <sub>3</sub>   | s <sub>2</sub>   | s <sub>1</sub>   | s <sub>0</sub>   |

| 2    | SE               | 0                | 0                | 0                | LBC              | 0                | 0                | 0                |

| 1    | CLS <sub>7</sub> | CLS <sub>6</sub> | CLS <sub>5</sub> | CLS <sub>4</sub> | CLS <sub>3</sub> | CLS <sub>2</sub> | CLS <sub>1</sub> | CLS <sub>0</sub> |

| 0    | 0                | ST <sub>6</sub>  | ST <sub>5</sub>  | ST <sub>4</sub>  | ST <sub>3</sub>  | ST <sub>2</sub>  | ST <sub>1</sub>  | ST <sub>0</sub>  |

PCD5008

8.5.6 ACTIVE RECEIVER STATES

#### 8.5.6.1 General

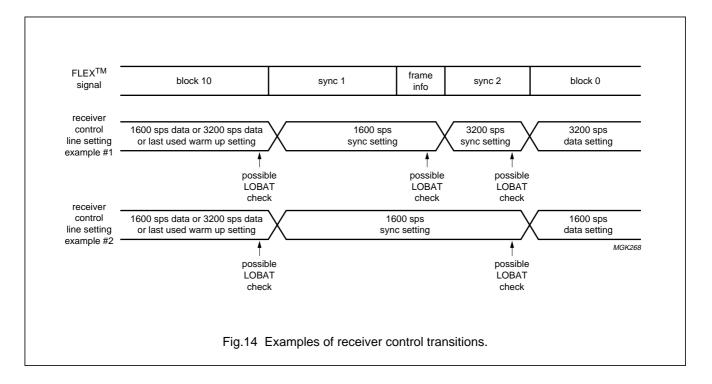

In addition to the warm-up and shut-down states, the PCD5008 has four active receiver states. When these settings are applied to the receiver control lines, the PCD5008 is decoding the EXTS1 and EXTS0 input signals. The timing of these signals and their duration depends on the FLEX<sup>™</sup> data stream. Because of this, there is no time setting associated with these settings (with the exception of the 3200 sps sync setting).

The four settings are as follows:

1600 sps sync setting: applied when the PCD5008 searches for a 1600 sps signal.

3200 sps sync setting: applied when the PCD5008 searches for a 3200 sps signal.

**1600 sps data setting:** applied after the PCD5008 has found the C or  $\overline{C}$  sync word in the sync 2 section of a 1600 sps frame.

**3200 sps data setting:** applied after the PCD5008 has found the C or  $\overline{C}$  sync word in the sync 2 section of a 3200 sps frame.

Figure 14 shows some examples of how these settings are used in the PCD5008.

### PCD5008

3200 sps data

1600 sps data

8.5.6.2 Receiver on setting packets (ID = 16H to 19H)

**LBC:** low battery check (Table 17). If this bit is set, the PCD5008 checks the status of the LOBAT port just before leaving this receiver sync setting state. Value after reset = 0.

**CLS:** control line setting (Table 17). This is the value to be output on the receiver control lines for this receiver sync setting state. Value after reset = 0.

**ST:** step time (Table 17). This sets the waiting time, before expecting good signals at EXTS1 and EXTS0 at the end of the warm-up sequence, after turning decoding on. The setting is in steps of 625  $\mu$ s. Valid values are: 625  $\mu$ s (ST = 01H) to 79.375 ms (ST = 7FH). Value after reset = 01H.

**LBC:** low battery check (Table 18). If this bit is set, the PCD5008 checks the status of the LOBAT port just before leaving this receiver on state. Value after reset = 0.

**CLS:** control line setting (Table 18). This is the value to be output on the receiver control lines (S0 to S7) for this receiver on state. Value after reset = 0.

**s:** setting number, see Tables 16 and 18 for the s names and values and location in the receiver on setting packet.

| Table 16 s names and values |                |                |                |               |  |  |  |  |

|-----------------------------|----------------|----------------|----------------|---------------|--|--|--|--|

| S <sub>3</sub>              | S <sub>2</sub> | s <sub>1</sub> | s <sub>0</sub> | SETTING NAME  |  |  |  |  |

| 0                           | 1              | 1              | 1              | 1600 sps sync |  |  |  |  |

0

1

8.5.7 FORCING RECEIVER LINES (ID = 0FH)

0

0

This packet (Table 19) enables host control over the receiver control line (S0 to S7) settings in all modes except reset. In reset, the receiver control lines are high impedance.

**FRS:** force receiver setting (Table 19). Setting a bit causes the associated CLS bit in this packet to override the internal receiver control settings on the corresponding receiver control line. Clearing a bit returns control of the corresponding receiver control line to the PCD5008. Value after reset = 0.

**CLS:** control line setting (Table 19). This bit setting is applied to the corresponding receiver control line if the associated FRS bit is set in this packet. Value after reset = 0.

| BYTE | BIT 7            | BIT 6            | BIT 5            | BIT 4            | BIT 3            | BIT 2            | BIT 1            | BIT 0            |

|------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 3    | 0                | 0                | 0                | 1                | 0                | 1                | 1                | 0                |

| 2    | 0                | 0                | 0                | 0                | LBC              | 0                | 0                | 0                |

| 1    | CLS <sub>7</sub> | CLS <sub>6</sub> | CLS <sub>5</sub> | CLS <sub>4</sub> | CLS <sub>3</sub> | CLS <sub>2</sub> | CLS <sub>1</sub> | CLS <sub>0</sub> |

| 0    | 0                | ST <sub>6</sub>  | ST <sub>5</sub>  | ST <sub>4</sub>  | ST <sub>3</sub>  | ST <sub>2</sub>  | ST <sub>1</sub>  | ST <sub>0</sub>  |

1

1

0

0

Table 17

3200 sps sync setting packet bit assignments

| Table 18 Receiver on setting | packet bit assignments |

|------------------------------|------------------------|

|------------------------------|------------------------|

| BYTE | BIT 7            | BIT 6            | BIT 5            | BIT 4            | BIT 3            | BIT 2            | BIT 1            | BIT 0            |

|------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 3    | 0                | 0                | 0                | 1                | S <sub>3</sub>   | S <sub>2</sub>   | S <sub>1</sub>   | s <sub>0</sub>   |

| 2    | 0                | 0                | 0                | 0                | LBC              | 0                | 0                | 0                |

| 1    | CLS <sub>7</sub> | CLS <sub>6</sub> | CLS <sub>5</sub> | CLS <sub>4</sub> | CLS <sub>3</sub> | CLS <sub>2</sub> | CLS <sub>1</sub> | CLS <sub>0</sub> |

| 0    | 0                | 0                | 0                | 0                | 0                | 0                | 0                | 0                |

Table 19 Receiver line control packet bit assignments

| BYTE | BIT 7            | BIT 6            | BIT 5   | BIT 4            | BIT 3            | BIT 2            | BIT 1            | BIT 0            |

|------|------------------|------------------|---------|------------------|------------------|------------------|------------------|------------------|

| 3    | 0                | 0                | 0       | 0                | 1                | 1                | 1                | 1                |

| 2    | 0                | 0                | 0       | 0                | 0                | 0                | 0                | 0                |

| 1    | FRS <sub>7</sub> | FRS <sub>6</sub> | FRS₅    | FRS <sub>4</sub> | FRS <sub>3</sub> | FRS <sub>2</sub> | FRS <sub>1</sub> | FRS <sub>0</sub> |

| 0    | CLS <sub>7</sub> | CLS <sub>6</sub> | $CLS_5$ | CLS <sub>4</sub> | CLS <sub>3</sub> | CLS <sub>2</sub> | CLS <sub>1</sub> | CLS <sub>0</sub> |

### PCD5008

#### 8.5.8 RECEIVER SHUT-DOWN SEQUENCE

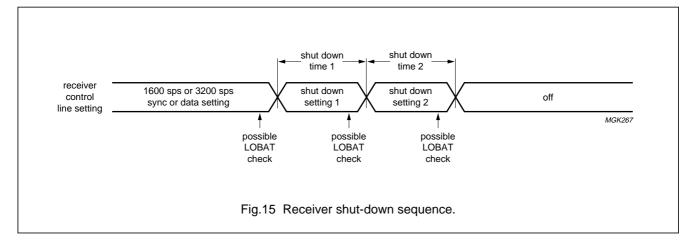

The PCD5008 allows up to 3 steps associated with shutting down the receiver. When the PCD5008 decides to turn off the receiver, the first shut-down setting, if enabled, is applied to the receiver control lines for the corresponding shut-down time. At the end of the last used shut-down time, the receiver off setting is applied to the receiver control lines. If the first shut-down setting is not enabled, the PCD5008 switches directly from the receiver on to the receiver off setting.

Figure 15 shows the receiver shut-down sequence when all shut-down settings are enabled. If the receiver is on or being warmed up when the decoder is turned off (by clearing the ON bit in the control packet), the PCD5008 immediately executes the receiver shut-down sequence. If the PCD5008 is executing the shut-down sequence when turned on (with the ON bit in the control packet set) the PCD5008 completes the shut-down sequence before starting the warm-up sequence.

#### 8.5.8.1 Receiver shut-down setting packets (ID = 1A to 1BH)

**SE:** step enable (Table 21). The receiver setting is enabled when the bit is set. If the bit is cleared then that step in the receiver shut-down sequence is disabled and all following steps are ignored. Value after reset = 0. **LBC:** low battery check (Table 21). If this bit is set, the PCD5008 checks the status of the LOBAT port just before leaving this receiver shut-down state. Value after reset = 0.

**CLS:** control line setting (Table 21). This is the value to be output on the receiver control lines (S0 to S7) for this receiver shut-down state. Value after reset = 0.

**ST**: step time (Table 21). This sets the duration time for receiver shut-down, until the next receiver state. The setting is in steps of 625  $\mu$ s. Valid values are 625  $\mu$ s (ST = 01H) to 39.375 ms (ST = 3FH). Value after reset = 01H.

**s:** setting number, see Tables 20 and 21 for the s names and values and location in the receiver shut-down packet.

#### Table 20 s names and values

| S | SETTING NAME |

|---|--------------|

| 0 | shut-down 1  |

| 1 | shut-down 2  |

| BYTE | BIT 7            | BIT 6            | BIT 5            | BIT 4            | BIT 3            | BIT 2            | BIT 1            | BIT 0            |

|------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 3    | 0                | 0                | 0                | 1                | 1                | 0                | 1                | S                |

| 2    | SE               | 0                | 0                | 0                | LBC              | 0                | 0                | 0                |

| 1    | CLS <sub>7</sub> | CLS <sub>6</sub> | CLS <sub>5</sub> | CLS <sub>4</sub> | CLS <sub>3</sub> | CLS <sub>2</sub> | CLS <sub>1</sub> | CLS <sub>0</sub> |

| 0    | 0                | 0                | ST <sub>5</sub>  | ST <sub>4</sub>  | ST <sub>3</sub>  | ST <sub>2</sub>  | ST <sub>1</sub>  | ST <sub>0</sub>  |

### Table 21 Receiver shut-down stages

### PCD5008

#### 8.6 Configuration of the FLEX<sup>™</sup> CAPCODE

#### 8.6.1 GENERAL

A CAPCODE specifies a decoder address, the collapse value of the address and whether single-phase, any-phase or all-phase address. The PCD5008 supports single-phase and any-phase operation. The FLEX<sup>™</sup> protocol provides a standard mechanism to derive phase and frame in which an address should be transmitted. If this mechanism is not used, a CAPCODE also specifies the phase and frame assigned to the address.

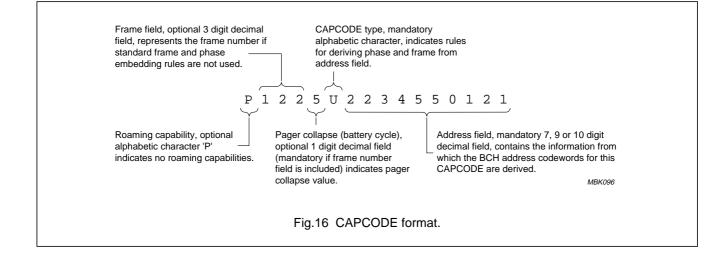

#### 8.6.2 CAPCODE FORMAT

The FLEX<sup>™</sup> CAPCODE consist of a series of decimal and alphabetic fields, see Fig.16 for the field definitions.

When the FLEX<sup>™</sup> standard pager collapse value of 4 (battery cycle of 16 frames) is used, the pager collapse field can be omitted.

The collapse value is a number between 0 and 7 and defines how often the decoding device looks for messages on the FLEX<sup>™</sup> channel. For a given collapse value b, the decoding device looks in every 2<sup>b</sup> frames. Thus an address with an assigned base frame of 3 and a collapse value of 5 typically looks for messages in frame 3 and every 32 frames thereafter (i.e. frames 3, 35, 67 and 99).

### PCD5008

#### 8.6.3 CAPCODE RANGES

A CAPCODE represents user addresses ranging from 1 to 5370810366. A short CAPCODE can have address values below 2031615 and are represented in the data stream by a single address codeword. Some short addresses have been reserved for special purposes: information service addresses, network addresses, temporary (group) addresses and operator messaging addresses. A long CAPCODE represents addresses situated above 2101248 subdivided into categories (uncoordinated, global, country) to allow different allocation schemes to coexist.

Table 22 defines the address usage assignment. All addresses not listed in this table are not defined and reserved for future use.

### Table 22 CAPCODE assignment table

| CAPCODE ADDRESS VALUE |            | DESCRIPTION                                                         |  |  |

|-----------------------|------------|---------------------------------------------------------------------|--|--|

| from                  | to         | DESCRIPTION                                                         |  |  |

| 00000                 | 00000      | illegal                                                             |  |  |

| 000000001             | 0001933312 | short addresses                                                     |  |  |

| 0001933313            | 0001998848 | illegal                                                             |  |  |

| 0001998849            | 0002009087 | reserved for future use                                             |  |  |

| 0002009088            | 0002025471 | Information service addresses                                       |  |  |

| 0002025472            | 0002029567 | network addresses                                                   |  |  |

| 0002029568            | 0002029583 | temporary addresses                                                 |  |  |

| 0002029584            | 0002029599 | operator messaging addresses                                        |  |  |

| 0002029600            | 0002031614 | reserved for future use                                             |  |  |

| 0002031615            | 0002101248 | invalid, not used                                                   |  |  |

| 0002101249            | 0102101250 | long address set 1-2 uncoordinated                                  |  |  |

| 0102101251            | 0402101250 | long address set 1-2 country; note 1                                |  |  |

| 0402101251            | 1075843072 | long address set 1-2 global; note 2                                 |  |  |

| 1075843073            | 2149584896 | long address set 1-3 global; note 2                                 |  |  |

| 2149584897            | 3223326720 | long address set 1-4 global; note 2                                 |  |  |

| 3223326721            | 3923326750 | long address set 2-3 country; note 1                                |  |  |